반도체 설계자산(IP) 플랫폼 전문회사 오픈엣지테크놀로지(이하 오픈엣지, 대표 이성현)가 7nm (나노미터, 1nm는 10억 분의 1m) 공정기술을 적용한 LPDDR5X, HBM3 메모리 표준을 지원하는 PHY(물리계층) IP 테스트 칩(반도체 시제품)을 최초로 개발했다.

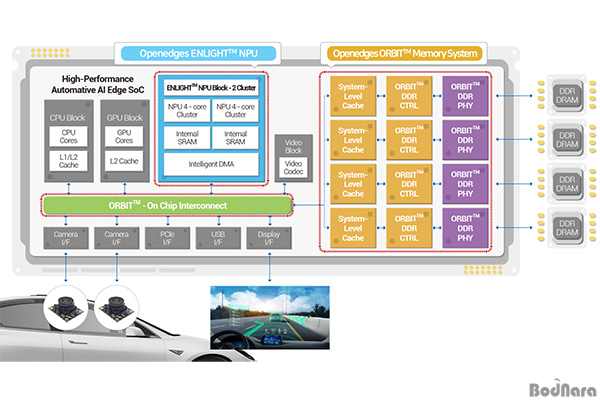

이번에 선행 개발한 최고 속도 8533 Mbps LPDDR5X용 메모리 표준을 지원하는 7nm 테스트 칩은 오픈엣지가 세계 최초로 선보였다. LPDDR5X 이전 메모리 표준과의 호환도 가능해 최종고객의 제품 DRAM의 선택의 폭도 넓혔다. 더불어, 독자적인 스케줄링 알고리즘에 따라 SoC(System-on-Chip)와 DRAM 간 고속 데이터 통신을 제어하는 오픈엣지의 DDR 메모리 컨트롤러 IP 제품과의 시너지로 저전력 DDR 메모리시스템에서 차별화된 성능을 제공할 수 있게 됐다.

LPDDR5X는 국제반도체표준협의기구 (Joint Electron Device Engineering Council, JEDEC)가 정한 LPDDR DRAM 표준 중 가장 최신의 표준으로 LPDDR5에 이은 차세대 고성능, 저전력 메모리다. 중앙집중 서버가 모든 데이터를 처리하는 클라우드 컴퓨팅과 달리 분산된 엣지 환경에서 실시간으로 처리하는 엣지 컴퓨팅(edge computing) 용도로 전력 소모 및 처리 속도를 최적화한 특장점이 있다.

|